curso: 2018-19

| Modelado e implementación en FPGAs de un conmutador de red de interconexión para un centro de proceso de datos |

Tecnologías Específicas

Ingeniería de Computadores

Descripcion y Objetivos

Los centros de proceso de datos (CPDs) son una infraestructura fundamental en la era del Big-Data, donde los datos almacenados en todo el planeta se van a multiplicar por diez en los próximos siete años. Dentro del CPD, la red de interconexión es un elemento esencial que debe garantizar alta productividad y baja latencia a las operaciones de comunicación de datos de las aplicaciones y servicios. Entre las cuestiones de diseño de la red de interconexión podemos encontrar, entre otros, la topología, los algoritmos de encaminamiento o el diseño de los componentes de red, como conmutadores e interfaces de red. En concreto, la arquitectura del conmutador es determinante para la configuración de topologías y algoritmos de encaminamiento eficientes, que garanticen unas altas prestaciones a la red de interconexión. Actualmente, diversas plataformas ofrecen diseños de conmutador abiertos, simples y compactos que pueden utilizarse tanto para aprender a diseñar elementos de red con un bajo nivel de detalle, como para investigar en futuras mejoras en la arquitectura del conmutador. Un ejemplo es la plataforma de desarrollo NetFPGA, formada por instituciones académicas y empresas de relevancia como Stanford y Cambridge, o Xilinx y Digilent, que ha generado una comunidad muy amplia en torno a proyectos y diseños de red en código abierto.

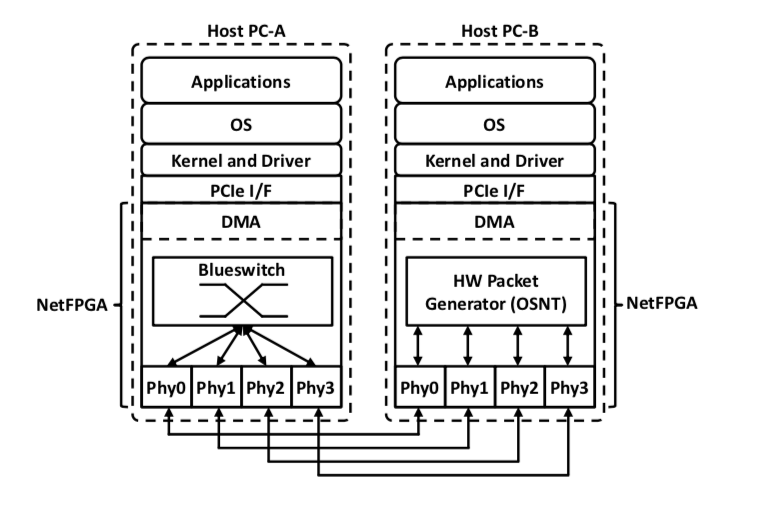

Este TFG propone el estudio, modelado e implementación en FPGAs de alguno de los modelos de conmutadores ofrecidos por NetFPGA (www.netfpga.org), como "Blueswitch" o "Reference Switch", y añadir alguna mejora en su arquitectura, como es el uso de colas específicas en los puertos de entrada u optimizaciones en el algoritmo de arbitraje. El prototipo experimental se construirá conforme al siguiente diagrama, mediante el uso de dos NetFPGA SUME de 4 puertos (una actuará de generador de tráfico y la otra incluirá el modelo de conmutador):

Los modelos de conmutador y de generación de tráfico están disponibles para la comunidad NetFPGA. Además, se realizará un estudio de las prestaciones ofrecidas por las arquitecturas de conmutador estudiadas.

Metodología y Competencias

Para alcanzar los objetivos del TFG, las actividades principales a realizar por el alumno son las siguientes (se indica el tiempo estimado de realización en meses, asumiendo una dedicación de 8 meses, 37,5 horas/mes y 300 horas de dedicación total al TFG):

1) Lectura de documentación sobre modelado de bajo nivel. En esta fase inicial, el alumno recibirá documentación para aprender nociones básicas sobre modelado de bajo nivel. El lenguaje de programación será Verilog, ya que la plataforma NetFPGA lo usa en sus diseños de código abierto (2 meses).

2) Montaje, conexión y configuración de la plataforma de prototipado basada en NetFPGA. Esta tarea consistirá en construir la plataforma de prototipado, descrita en la figura anterior, y probar que funciona mediante un conjunto de diseños de conmutador existentes como "Blueswitch" o "Reference Switch", y también de tests y pruebas de regresión disponibles en la plataforma NetFPGA. El hardware está disponible en el laboratorio del grupo RAAP, en el I3A, donde el alumno tendrá asistencia técnica por parte del técnico del grupo, así como un espacio de trabajo propio para desarrollar el proyecto, incluyendo la ubicación del prototipo. (2 meses).

3) Modelado e implementación de mejoras sencillas al modelo de conmutador. Esta tarea consiste en la implementación de alguna mejora en el modelo de conmutador dentro del prototipo construido en la tarea anterior, cuya dificultad sea asumible por el alumno, de acuerdo a los conocimientos adquiridos en la tarea 1. Por ejemplo, el modelo de conmutador "Reference Switch" del NetFPGA incluye colas simples en los puertos de entrada. Una mejora que se podría realizar es el uso de varias colas por puerto de entrada, para evitar los efectos de la contención dentro del conmutador. Esta es una de las mejoras que el alumno puede introducir en el modelo de conmutador, aunque, como se ha comentado anteriormente, se estudiarán otras opciones que sean factibles en tiempo y forma. Finalmente, se realizará un breve estudio de prestaciones para analizar el rendimiento conseguido con la mejora introducida (3 meses).

4) Documentación de los resultados y redacción de la memoria de TFG (1 mes).

Competencias adquiridas:

- Capacidad de diseñar y construir sistemas digitales, incluyendo computadores, sistemas

basados en microprocesador y sistemas de comunicaciones.- Capacidad de analizar y evaluar arquitecturas de computadores, incluyendo plataformas

paralelas y distribuidas, así como desarrollar y optimizar software para las mismas.- Capacidad de diseñar e implementar software de sistema y de comunicaciones.

- Capacidad para analizar, evaluar, seleccionar y configurar plataformas hardware para el

desarrollo y ejecución de aplicaciones y servicios informáticos.- Capacidad para diseñar, desplegar, administrar y gestionar redes de computadores.

Medios a utilizar

Los medios a utilizar para el desarrollo del TFG son los siguientes:

- 2x NetFPGA SUME conectadas a dos ordenadores tipo PC, según el modelo de la figura anterior, instalados con SO Linux (disponibles en el grupo RAAP del I3A).

- Código fuente de los modelos ofrecidos por la plataforma NetFPGA.

- Ordenador tipo PC.

Bibliografía

La bibliografía básica para el desarrollo del TFG es la siguiente:

- Manuales de desarrollador en Verilog.

- Documentación y manuales sobre el entorno NetFPGA.

- https://github.com/NetFPGA/NetFPGA-SUME-public/wiki/NetFPGA-SUME-Reference-Learning-Switch

- Diversos libros y artículos sobre redes de interconexión.

Toda la bibliografía está disponible.

TutoresGARCÍA GARCÍA, PEDRO JAVIER ESCUDERO SAHUQUILLO, JESUS | AlumnoMORÁN MUÑOZ, ANTONIO |